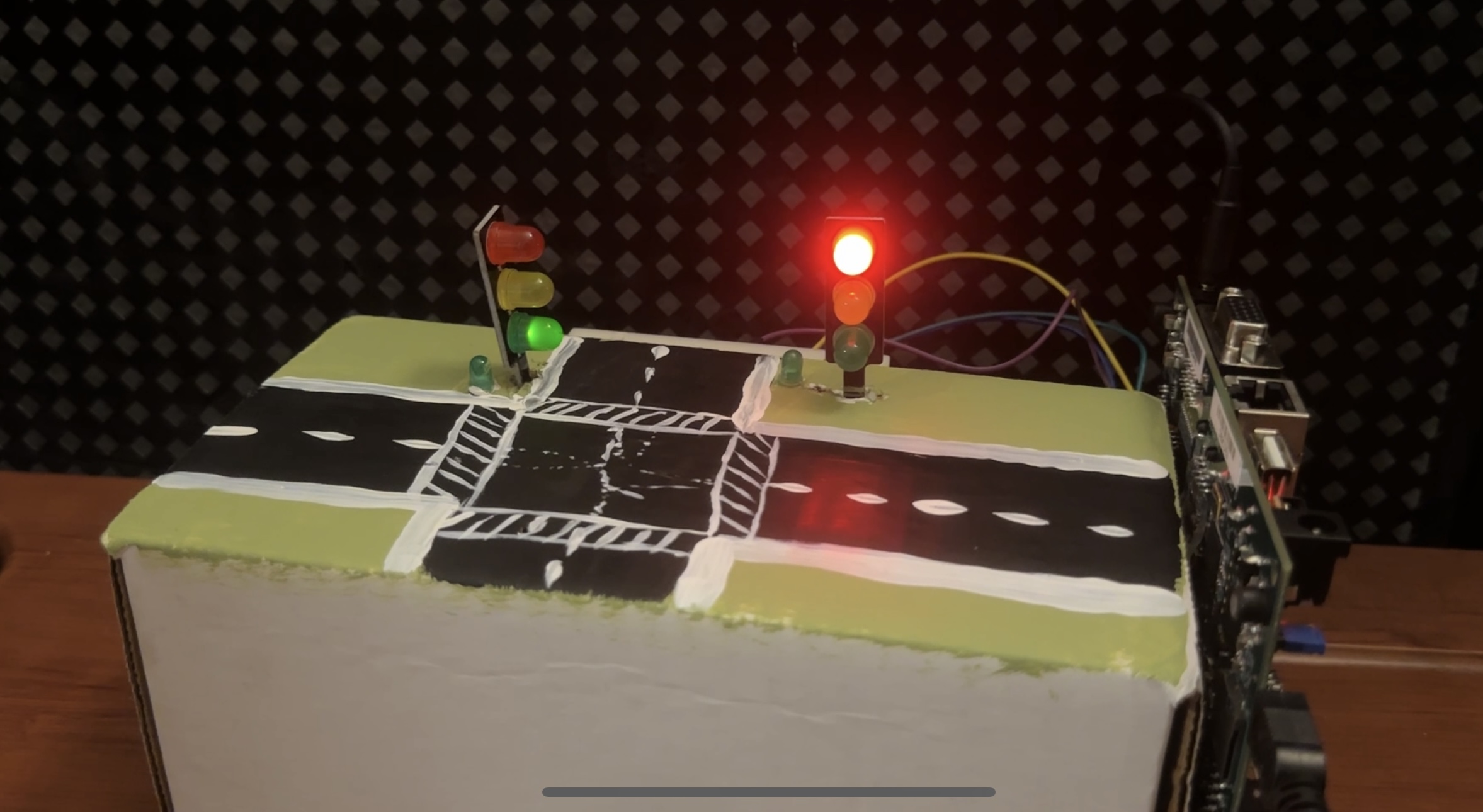

Traffic Light Simulator and Controller (FPGA)

Final project demonstration for my ECE 3300L (Digital Logic Design with Verilog). For the Verilog code check the Github Repository.

Cal Poly Pomona student

Computer Engineering

Computer Engineering Student from Cal Poly Pomona

I am a dedicated and innovative computer engineering student with a strong foundation in FPGA development, digital logic design, and micro-controller programming. Through internships, academic projects, and previous work experience, I have developed a robust set of skills in software & hardware engineering, business management, and an eagerness to contribute to innovative and challenging projects in the industry. I am known for my problem-solving skills, ability to work collaboratively in team settings, and a commitment to continuous learning and professional development.

A collection of projects and laboratories that have been completed.

Final project demonstration for my ECE 3300L (Digital Logic Design with Verilog). For the Verilog code check the Github Repository.

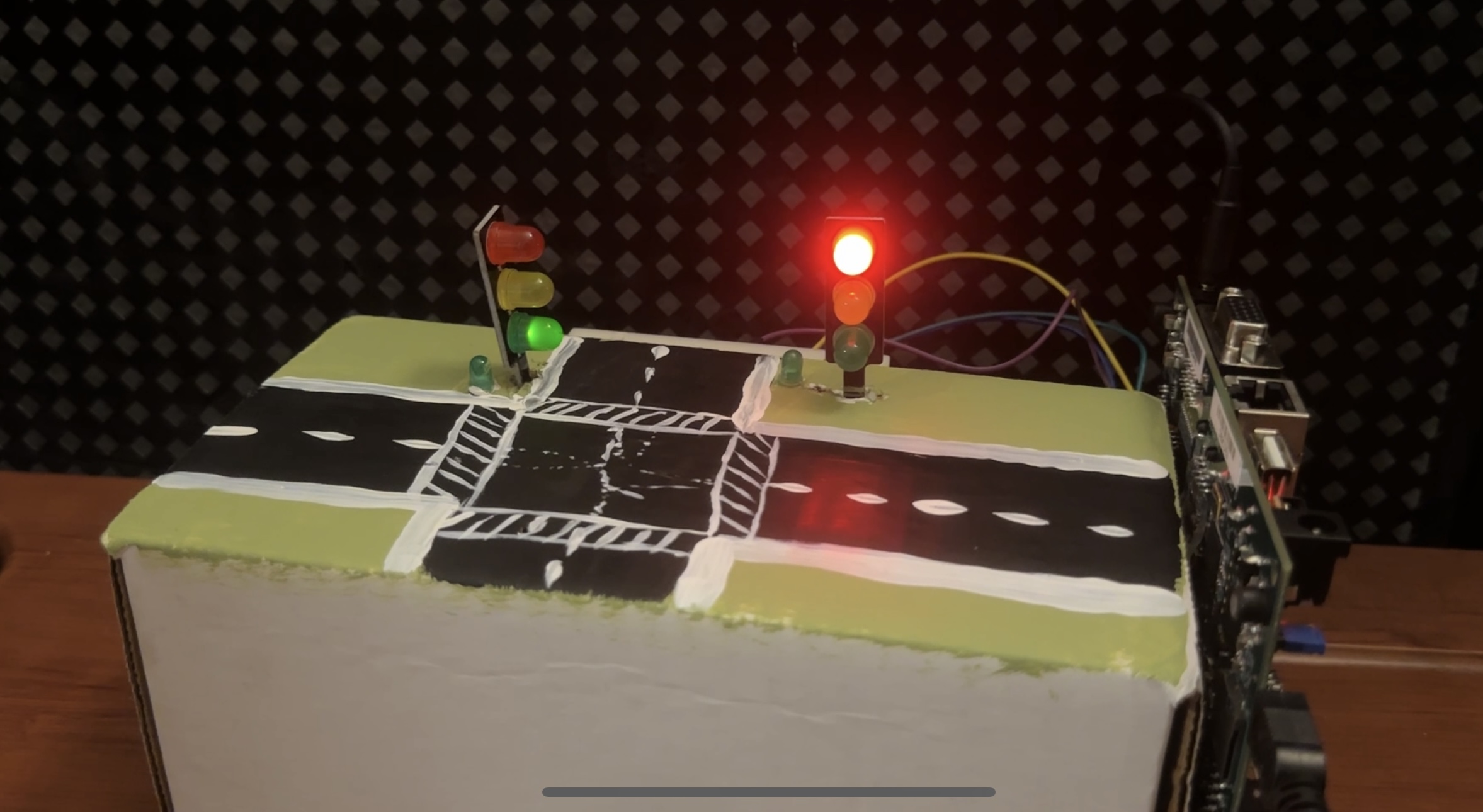

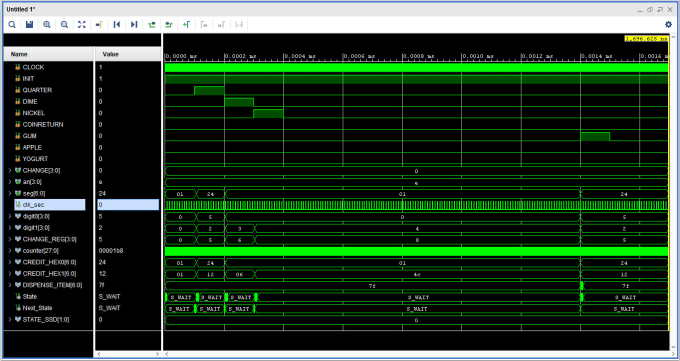

Collection of various projects in Verilog HDL and implementation in an FPGA board. (Nexys A7-100T).

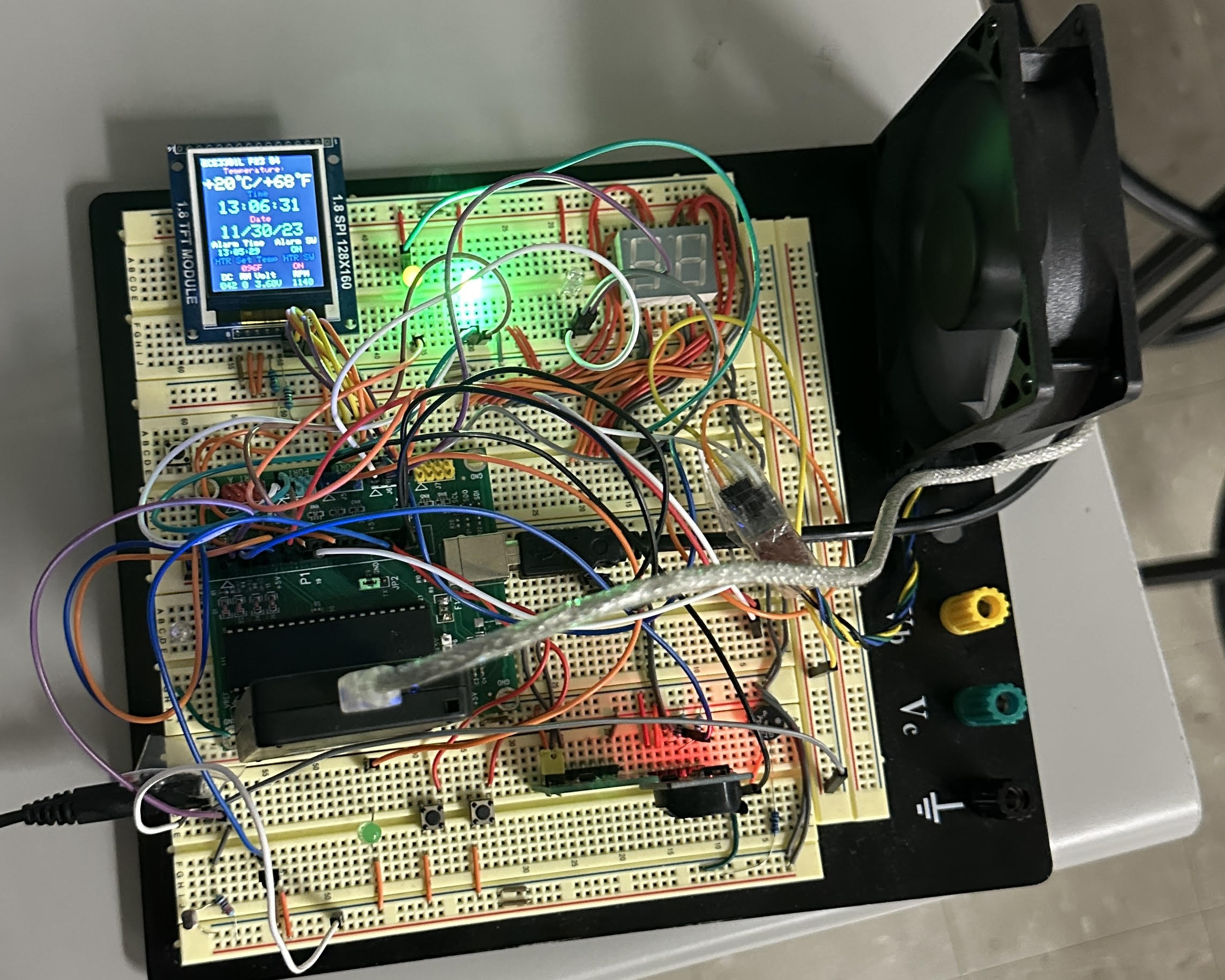

Implemented the PIC18F4321 microcontroller as the central processing unit for an integrated control panel system that emulated an AC unit with automated temperature control depending on ambient temperature and a TFT display that showed time, temperature, and mode dependent of ambient light.

Executed a Birdwatcher app at Cal State LA using the Intel AI DevCloud and OpenVINO inference engine for machine learning. Developed the program in Python and implemented the use of Linux commands.

As the media chair, I created and completely redesigned the IEEE, Cal Poly Pomona chapter and implemented a dynamic calendar to show future workshops and events, as well as an "events" page to document media from previous workshops and events.